Page 51 - Electrical & Electronic Engineering Brochure 2024 WEB

P. 51

FPGA Training Course BL0580 Arduino GSM Training Course BL0521

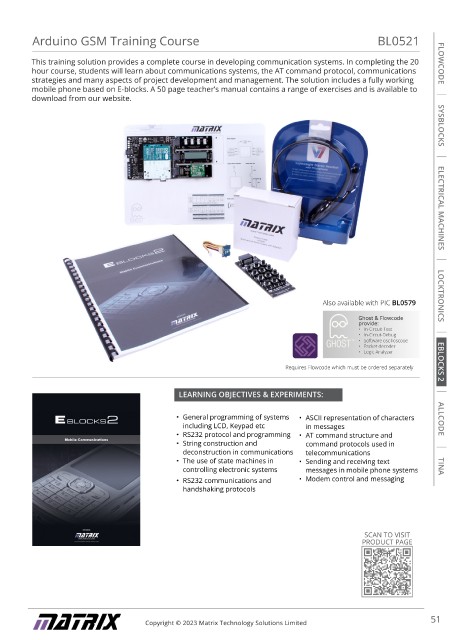

This training solution provides a complete 40 hour course in the techniques of developing projects based on This training solution provides a complete course in developing communication systems. In completing the 20 FLOWCODE

FPGAs using either Verilog or VHDL using an Altera FPGA and the free version of the Quartus design software, hour course, students will learn about communications systems, the AT command protocol, communications

which requires registration with Altera. The equipment is ideal for learning and for project work and students strategies and many aspects of project development and management. The solution includes a fully working

can go on to develop more advanced projects which might even include embedding NIOS processors. A full mobile phone based on E-blocks. A 50 page teacher’s manual contains a range of exercises and is available to

FLOWCODE

instructors’ manual is available to download from our website. download from our website. SYSBLOCKS

SYSBLOCKS

ELECTRICAL MACHINES

ELECTRICAL MACHINES

Also available with PIC BL0579 LOCKTRONICS

Ghost & Flowcode

provide:

LOCKTRONICS

• In-Circuit-Test

• In-Circut-Debug

• Software oscilloscope

• Packet decoder

• Logic Analyzer

Quartus Software Example Requires Flowcode which must be ordered separately EBLOCKS 2

EBLOCKS 2

LEARNING OBJECTIVES & EXPERIMENTS: LEARNING OBJECTIVES & EXPERIMENTS:

• FPGA design techniques decoders, parity checkers, adders, • General programming of systems • ASCII representation of characters ALLCODE

• Quartus development subtractors, multipliers including LCD, Keypad etc in messages

environment: top down and • Sequential logic circuits: SR, D, JK • RS232 protocol and programming • AT command structure and

ALLCODE

bottom up projects flip flops, asynchronous up, down • String construction and command protocols used in

• VHDL design language and BCD counters, synchronous deconstruction in communications telecommunications

• Verilog design language binary up and down counters, state • The use of state machines in • Sending and receiving text TINA

• Combinational logic circuits: machines controlling electronic systems messages in mobile phone systems

TINA

simple circuits, encoders, • Project work • RS232 communications and • Modem control and messaging

handshaking protocols

SCAN TO VISIT SCAN TO VISIT

PRODUCT PAGE PRODUCT PAGE

50 Copyright © 2023 Matrix Technology Solutions Limited Copyright © 2023 Matrix Technology Solutions Limited 51